ZYNQ在AD7606AD7616加持下的能源电力方案,实现同步采样

1 AD7606/AD7616介绍

AD7606是ADI公司的16位、8通道同步采样AD芯片,并行采样率高达200KSPS(AD7616是16位、16通道、1MSPS)。在电力线路测量和保护系统中,需要对多相输配电网络的大量电流和电压通道进行同步采样,AD7606是目前电力系统中最常用的ADC采样芯片之一。

AD7606片上集成模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器、16位电荷再分配逐次逼近型ADC内核、数字滤波器、2.5V基准电压源及缓冲、高速串行和并行接口。AD7606采用5V单电源供电,不再需要正负双电源,并支持±10V或±5V的双极性信号输入。所有通道均能以高达200KSPS的速率进行采样,同时输入端箝位保护电路可以承受最高达±16.5V的电压。

目前AD7606已广泛应用于电力线路检测和保护系统、多项电机控制、仪器仪表和控制系统、多轴定位系统核数据采集系统(DAS)。

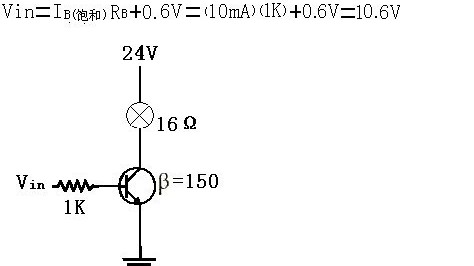

图 1

图 2

图 3

图 4

2 ZYNQ SoC在能源电力领域方案优势

(1) 采用Xilinx Zynq-7000 SoC高性能低功耗处理器,集成PS端单核/双核ARM Cortex-A9 + PL端Artix-7架构可编程逻辑资源。

(2) 可通过PL端Artix-7架构可编程逻辑资源按需扩展外部功能接口,只要资源满足,理论上无数量限制。典型应用:CAN(4路)、千兆以太网(2路)、百兆以太网(4路)、UART(12路)、SPI(5路),特别是可通过外接多片AD芯片(AD7606/AD7616),实现16/32/64路AD同步采样。

(3) OpenAMP框架可实现双核ARM Cortex-A9非对称使用方案,从而使双核ARM实现分别跑两个系统:一个ARM Cortex-A9跑Linux,一个ARM Cortex-A9作为实时核跑RTOS(FreeRTOS)或者裸机。实时核与FPGA端进行低延时的高速数据交换与实时通讯控制,从而满足低延时的实时任务要求。而跑Linux的 ARM核作为更上层应用,处理更复杂的业务事务。

(4) 外部可扩展LCD显示与触摸屏控制,分辨率支持2048*2048,支持1080P高清视频播放与HDMI视频输出,满足多种屏幕与人机交互的功能需求;

3 AD7606在ZYNQ平台的应用

创龙科技在Zynq-7000、OMAP-L138/C6748/F2837x + Spartan-6等平台均提供了AD7606的开发案例。

创龙科技基于Zynq-7010/7020处理器设计的工业评估板TLZ7x-EasyEVM-S,它由核心板+底板构成。用户使用核心板进行二次开发时,仅需专注上层运用,降低了开发难度和时间成本,可快速进行产品方案评估与技术预研。

图 5 TLZ7x-EasyEVM-S评估板(邮票孔)

图 6 TLZ7x-EasyEVM评估板

本文以Zynq-7000工业评估板TLZ7x-EasyEVM-S为例,讲解ad7606_fft例程。

3.1 功能说明

PL端采集AD7606的8通道AD信号,采样率为200KSPS,并通过DMA IP核将数据缓存到PS端DDR中(每通道各采样4096个点),再通过FFT IP核将数据进行FFT运算,然后将FFT运算结果保存到PS端DDR中,最后通过ILA显示第一个通道的原始波形和FFT运算结果波形。

备注:由于本案例消耗逻辑资源较多,因此本案例不支持xc7z010,仅支持xc7z020。

3.2 案例框图

图 7

点击BLOCK DESIGN开发界面下的"Address Editor"选项,可查看IP核分配的地址,PS端可通过对应地址对IP核进行控制。

图8

3.3 AD7606模块

该模块控制AD7606对8通道AD信号按200K采样率进行采集,并将数据通过AXI4-Stream接口进行发送。

图 9

进入BLOCK DESIGN开发界面,双击模块框图,可查看模块的具体配置信息。采样率为200KSPS,模块工作时钟为50MHz。

图 10

备注:模块、IP核简介可扫描文末二维码下载详细资料。

3.4 案例测试

将TLP2P-PinBoard转接板接到评估板CON8接口,再将AD模块TL7606P与转接板连接。

图 11

进入评估板文件系统,执行如下命令配置PS-PL电平转换寄存器。

Target# devmem 0xf8000900 w 0xf

图 12

使用下载器加载PL端程序以及和PL端程序同目录下的.ltx文件。

图 13

在ila_1的Trigger Setup窗口点击按钮,双击axi_dma_0_m_axis_mm2s_tvalid将其添加为触发信号。

图 14

将Value的值改成R,设置为上升沿触发。

图 15

右击Channel_1_data[15:0],点击“Waveform Style -> Analog”将通道1的原始信号设置为模拟波形。

图 16

右击Channel_1_data[15:0],点击“Radix -> Signed Decimal”设置数据为有符号类型。

图 17

参考上面的步骤,在ila_2将axi_dma_1_m_axis_mm2s_tvalid添加为触发信号,设置为上升沿触发,将FFT IP核输出数据的实部和虚部信号分别设置为模拟波形,并设数据为有符号类型。

图 18

图 19

使用信号发生源向TL7606P模块的8个通道分别输入信号,本案例测试的输入信号是频率为2KHz、峰峰值为3.3Vpp的正弦波。

将案例“sw\linux_system\image\”目录下所有脚本文件拷贝至评估板文件系统。执行如下命令使能axi_dma_0的S2MM通道,将数据采集到PS端DDR中。

Target# ./axi_dma_0_ad7606_to_ddr.sh

执行如下命令使能axi_dma_1的S2MM通道(FFT转换后数据保存到PS端DDR),等待FFT IP核工作。

Target# ./axi_dma_1_fft_to_ddr.sh

执行如下命令使能axi_dma_0的MM2S通道,把原始数据从DDR送到FFT IP核。

Target# ./axi_dma_0_ddr_to_fft.sh

执行如下命令使能axi_dma_1的MM2S通道,把FFT转换后的数据从DDR送到ILA显示。

Target# ./axi_dma_1_ddr_to_ila.sh

图 20

axi_dma_0_ad7606_to_ddr.sh

配置axi_dma_0的S2MM通道,将数据传输到DDR。

图 21

配置好DMA后,配置axi gpio输出1,设置adc_enable为1,使能ADC转换。需确保DMA已配置好,再使能ADC转换并进行数据传输。

图 22

axi_dma_0_ddr_to_fft.sh

配置axi_dma_0的MM2S通道,将DDR中的数据通过AXI4-Stream发送给FFT IP核。

图 23

ila_1原始波形

输入信号是频率为2KHz、峰峰值为3.3Vpp(电压幅值为1.65V)的正弦波。一共4096个采样点,每个采样点4个时钟周期,即4096=16384/4。

图 24

图 25

波峰值为+10729,波谷值为-10794,峰峰值=(10729 + 10794)/(2^16)x10V≈3.2841V,采样范围为±5V。

图 26 波峰值

图 27 波谷值

Ila_2 FFT波形

Channel_1_fft_IM_Dout为虚部,Channel_1_fft_RE_Dout为实部。

图 28

频率计算

FFT变换点数N=4096,AD采样率Fs为200KSPS。某点n所表示的频率Fn=(n-1)*(Fs/N)(n>=1)。当n=1时,Fn为0,由于第一点表示的是直流分量,因此频率为0,幅值也为0,该正弦波无直流分量。

从下图可知,在第164个周期(即第42个采样点)处出现信号,则信号频率Fn=(42-1)*(Fs/N)=41*200KHz/4096=2001.95Hz,与原始信号频率2KHz基本一致。

图 29

幅值(波峰值)计算

某个点的幅值An=(根号(实部^2 + 虚部^2))*压缩倍数/(N/2),则信号幅值An=(根号(4448^2 + 3008^2))x4096/4096x2≈10739.23,信号电压幅值=10739.23/(2^16/2)x5V≈1.64V,与原始信号电压幅值1.65V基本一致。

查看原始数据

每个采样点32bit(包括实部和虚部),每个通道的数据的地址依次递增,从地址0x19000000开始。

Target#devmem 0x19000000 //查看V1通道原始数据

Target#devmem 0x19000004 //查看V2通道原始数据

Target#devmem 0x19000008 //查看V3通道原始数据

Target#devmem 0x1900000c //查看V4通道原始数据

Target#devmem 0x19000010 //查看V5通道原始数据

Target#devmem 0x19000014 //查看V6通道原始数据

Target#devmem 0x19000018 //查看V7通道原始数据

Target#devmem 0x1900001c //查看V8通道原始数据

图 30 查看V1通道原始数据

查看FFT数据

每个采样点32bit(包括实部和虚部),每个通道的数据的地址依次递增,从地址0x19100000开始。

Target#devmem 0x19100000 //查看V1通道FFT数据

Target#devmem 0x19100004 //查看V2通道FFT数据

Target#devmem 0x19100008 //查看V3通道FFT数据

Target#devmem 0x1910000c //查看V4通道FFT数据

Target#devmem 0x19100010 //查看V5通道FFT数据

Target#devmem 0x19100014 //查看V6通道FFT数据

Target#devmem 0x19100018 //查看V7通道FFT数据

Target#devmem 0x1910001c //查看V8通道FFT数据

图 31 查看V1通道FFT数据

如需案例源码或详细案例说明,可在评论区留言,进行分享。

非对称的ARM双系统,如何实现工业产品的低延时——基于ZYNQ

现代工业设备系统要求越来越复杂,既要强大的多任务的事务处理能力,又需要低延时实时任务处理能力的需求,特别是工业自动化控制领域(如数控机床、机械臂)、电力监测领域(如DTU、继保设备、一二次融合设备)等应用场景尤为迫切。为了满足日益复杂的系统要求,基于Xilinx Zynq-7020/7010实现的双系统解决方案。Xilinx Zynq-7020/7010是一款集成双核ARM Cortex-A9 + Artix-7 FPGA架构的单芯片SoC,它的OpenAMP框架可实现双核ARM Cortex-A9非对称使用方案,从而使双核ARM实现分别跑两个系统:一个ARM Cortex-A9跑Linux,一个ARM Cortex-A9作为实时核跑RTOS(FreeRTOS)或者裸机。实时核与FPGA端进行低延时的高速数据交换与实时通讯控制,低延时的实时任务要求。而跑Linux的 ARM核作为更上层应用,处理更复杂的业务事务。

Xilinx Zynq-7020/7010单芯片SoC方案配合双系统的应用为工业控制、电力一二次融合设备、医疗电子、测试测量、汽车电子、通信等应用是更灵活、更具优势的解决方案。

1、echo_test案例

1.1 案例功能

案例功能:CPU0使用RPMsg向CPU1发送数据,CPU1接收到数据后再使用RPMsg向CPU0回传数据。CPU0对回传的数据进行验证,并输出验证结果。

1.2 操作说明

将CPU1裸机或FreeRTOS可执行文件复制到评估板文件系统“/lib/firmware/”目录下,并执行如下命令加载CPU1程序。

Target# echo echo_test.elf > /sys/class/remoteproc/remoteproc0/firmwareTarget# echo start > /sys/class/remoteproc/remoteproc0/state

图 3

执行如下命令加载RPMsg驱动,并在“/dev/”目录下生成RPMsg设备节点。Target# modprobe rpmsg_user_dev_driver

图 4

将CPU0应用程序可执行文件复制到评估板文件系统,并执行如下命令通过RPMsg与CPU1进行通信。

Target# ./echo_test

图 5

输入1,并按回车键进行测试。

图6

图7

输入2,并按回车键退出测试。

图 8

执行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

图 9

2、matrix_multiply案例

2.1 案例功能

案例功能:CPU0随机生成两个矩阵并使用RPMsg向CPU1发送数据,CPU1接收到数据后进行矩阵乘法运算,再使用RPMsg向CPU0回传运算结果,然后CPU0通过串口终端输出运算结果。

2.2 操作说明

将CPU1裸机或FreeRTOS可执行文件复制到评估板文件系统“/lib/firmware/”目录下,并执行如下命令加载CPU1程序。

Target# echo matrix_multiply.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

图 10

执行如下命令加载RPMsg驱动,并在“/dev/”目录下生成RPMsg设备节点。

Target# modprobe rpmsg_user_dev_driver

图 11

将CPU0应用程序可执行文件复制到评估板文件系统,并执行如下命令通过RPMsg与CPU1进行通信。

Target# ./mat_mul_demo

图 12

输入1,并按回车键进行测试。

图 13

输入2,并按回车键退出测试。

图 14

执行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

图 15

3、内存分配说明

512MByte DDR容量版本核心板的内存地址分配如下:

表 1

1GByte DDR容量版本核心板的内存地址分配如下:

表 2

如需修改CPU1程序(OpenAMP-remote app)内存地址空间范围,可通过更改设备树文件tlz7x-easyevm-s.dts、资源表rsc_table.c及链接文件lscript.ld对内存地址空间进行重新分配。三者需同步修改并保持一致,以确保固件程序链接地址与设备树配置的elf_ddr_0对应。所使用的资源(内存和virtio设备资源)不能超出设备树文件配置的内存范围。

图 16设备树文件tlz7x-easyevm-s.dts配置

图 17设备树文件tlz7x-easyevm-s.dts配置

图 18 CPU1程序资源表rsc_table.c配置

图 19 CPU1程序链接文件lscript.ld配置

上述推文中的案例是在创龙科技(Tronlong)基于Zynq-7010/7020处理器设计的两款工业评估板——TLZ7x-EasyEVM、TLZ7x-EasyEVM-S上实现的,它由核心板+底板构成。

图 20 TLZ7x-EasyEVM硬件资源框图

图 21 TLZ7x-EasyEVM硬件资源框图

图 22 TLZ7x-EasyEVM-S硬件资源框图

图 23 TLZ7x-EasyEVM-S硬件资源框图

相关问答

创龙科技怎么样?创龙科技专注于DSP、ARM、FPGA多核异构技术开发,是TI、Xilinx中国官方合作伙伴,产品线覆盖TIC6000/Sitara/DaVinci/C2000、XilinxZYNQ/KINTEX...