ICCAD2021落幕,AI设计芯片趋势明显,港中文Front-End最佳论文奖

机器之心专栏

目前芯片是备受关注的研究领域,EDA 是重点方向之一。中国在 EDA 领域薄弱,但港中文在 EDA 研究方面很有实力,CS Ranking 近年来都位居前列,今年更是跃居第一。本文是港中文余备教授参加 ICCAD 2021 的见闻和有感,以专业视角给出了值得关注的趋势,也即 ML for EDA(或者EDA的人工智能化趋势)。他们也获得今年前端 track 最佳论文。

为了方便读者更为细致的了解 ML for EDA,11月10日-11日,我们请到港中文EDA团队带来线上分享,介绍 4 篇他们在 ICCAD 2021 的最新工作。

近日,EDA领域的世界顶级会议之一 ICCAD 2021 大会以线上形式成功举办。

International Conference on Computer-Aided Design (ICCAD)是 IEEE 和 ACM 两大组织联合发起的电子设计自动化(Electronic Design Automation, EDA)领域的顶级会议。自 1982 年创办以来,迄今已经举办了 40 届。

由于疫情原因,今年的 ICCAD 依然采用线上会议的方式举办,会议从 11月1日 至 4日 共四天。ICCAD 2021 收到了全球范围内的 514 篇投稿,最终 121 篇论文被收录(23.5%的录取率),竞争十分激烈。

在 ICCAD 2021 讨论热点的词云中,可以看到此次大会频率较高的关键词:神经网络、EDA关键步骤研究、加速器。另据会议官方数据统计,相比往年,神经网络和深度学习、仿真设计验证、神经形态计算、生物芯片等领域投稿论文数量激增。

最佳论文奖

为了纪念 William J. McCalla 博士对计算机辅助电路设计及仿真技术的发展以及 ICCAD 会议的开创性贡献,会议官方特别设立了 William J. McCalla 最佳论文奖。该奖项由 IEEE 电子设计自动化委员会(IEEE CEDA)和 ACM 设计自动化特别兴趣小组(ACM SIGDA)联合发起,由 ICCAD 最佳论文和最具影响力奖评选委员会评选,于 2000 年首次颁发。

William J. McCalla 最佳论文奖共设立年度最佳论文奖两名(Front-end和Back-end),以及十年回顾最具影响力论文奖一名。其中,年度最佳论文奖将分别授予涵盖集成电路设计流程前端和后端的研究论文。

2021年ICCAD Front-End最佳论文奖授予了《BOOM-Explorer: RISC-V BOOM Microarchitecture Design Space Exploration Framework》,第一作者是就读于香港中文大学计算机科学与工程系的博士生白晨,导师为余备教授和黄定发教授。

论文链接:

http://www.cse.cuhk.edu.hk/~byu/papers/C122-ICCAD2021-DSE-BOOM.pdf

这篇获奖论文研究了基于机器学习技术进行 CPU 微架构设计空间探索的方法,实现了在同一工艺下寻找一系列在功耗和性能上实现帕累托最优的微架构。在后摩尔时代 CPU 设计中,工艺演进对提高 CPU 性能、降低其功耗的红利愈来愈有限,因此,CPU 设计人员希望能寻找到理想的微架构来更好地平衡性能和功耗。微架构是对指令集(ISA)的实现,包含了诸如 CPU 取指前端,解码,计算单元,载入储存单元等模块。这些模块可以在 CPU 设计时进行参数化,如对缓存结构,解码宽度,乘除单元并行数,分支预测器等。由于现代 CPU 设计变得愈加复杂,架构师的经验不能很好用来迁移到新设计上以确定这些参数。为了在一个确定的微架构设计空间中快速寻找帕累托设计,因此,本文基于 RISC-V微处理器提出一种能嵌入目标设计的微架构先验知识的设计空间探索算法用来解决这一问题。

从左至右:白晨、余备教授、黄定发教授。本次的Back-End最佳论文奖授予了《Analytical Modeling of Transient Electromigration Stree based on Boundary Reflections》,第一作者是来自明尼苏达大学的 Mohammad Abdullah Al Shohel。

这篇论文提出了一种瞬态电迁移应力建模算法。电迁移在多段互联上的传统失效测试方法是基于 Black 方程的 Blech 标准。考虑到应力在多个互联段上具有累积效应,而传统方法是独立地分析每个互联段,导致了不准确的分析结果。该论文创新性地引入了应力流边界反射的概念,认为在有限多互联段中的瞬态应力行为可以采用物理波动来解释。该论文基于应力流边界反射的概念,提供了一个用于推导出具有任意数量互联段的瞬态电迁移应力的分析表达式框架。在大型供电网络基准测试中,该方法对比于基于有限元法的求解器 COMSOL 具有更高的准确度和更快的求解速度。

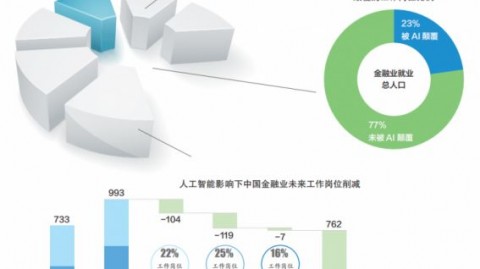

二、EDA的科研趋势:AI x EDA

当前,集成电路产业已成为衡量国家综合国力的重要战略指标。其中 EDA 工具是集成电路产业的基础工业软件,也是我国集成电路中受美国制约最严重的环节之一,可谓是我国集成电路产业的「命门」。为了支撑我国目前正在如火如荼进行的「新基建」建设,以及实现未来科技实力大幅度提升的目标,作为集成电路产业最基础的支撑,发展独立自主可控的 EDA 工具已经迫在眉睫。一方面,人工智能技术(包括算法上的改进,与计算平台的演进)给 EDA 带来了新的解决方案;另一方面,EDA 技术的发展,也促进了人工智能技术在芯片设计和制造上的不断迭代与改进。以下精选 5 篇论文,很好的反应了 AI 与 EDA 结合的大趋势。

Paper A:Overcoming the Memory Hierarchy Inefficiencies in Graph Processing Applications

作为大数据时代的重要应用,图计算在传统处理器和内存架构上的性能并不高效。其性能瓶颈通常体现在两个方面:对于片上内存而言,随机的访存模式大幅降低了缓存命中;对于片外内存而言,细粒度的数据读取也拉低了DRAM主存的带宽利用率。

为此,UCSB 谢源教授团队设计了专用于图的内存架构:G-MEM。一方面,其使用了scratchpad替代缓存,并相应的提出了针对图结构中“热点”数据的管理算法,在与缓存相同大小的情况下提升了约 10% 的命中率。另一方面,其重新设计了 DRAM 的通道架构,并使用了多个独立控制器以支持细粒度的访存。相比于传统处理器,G-MEM 在多个图任务下提升了 2.6 倍的性能。

Paper B: Automatic Routability Predictor Development Using Neural Architecture Search

机器学习技术的兴起激发了其在电子设计自动化 (EDA) 中的应用热潮,并有助于提高芯片设计的自动化程度。然而,手工制作的机器学习模型需要大量的专业知识和巨大的工程消耗。在这项工作中,Duke 大学陈怡然教授课题组和 Texas A&M 大学胡江教授课题组利用神经架构自动搜索 (NAS) 来自动开发用于可绕线性预测的高质量神经网络架构。该搜索方法支持各种卷积操作和高度灵活的连接,使得神经网络架构与以前所有的人工模型明显不同。在大型数据集上的实验结果表明,生成的自动生成的神经网络架构明显优于多个具有代表性的人工设计的模型架构。此外,与人工模型容易花费数周时间开发相比,高效的 NAS 方法仅用 0.3 天就完成了整个自动搜索过程。

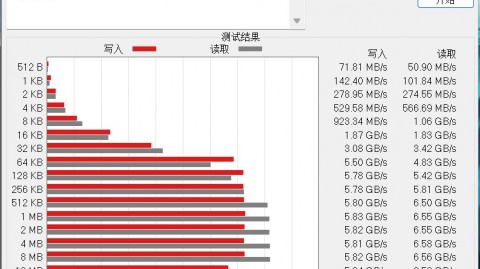

Paper C: pGRASS-Solver: A Parallel Iterative Solver for Scalable Power Grid Analysis Based on Graph Spectral Sparsification

随着集成电路与系统的发展,供电网络的规模越来越庞大,使得对其分析、计算其节点电压成为一个严峻的挑战。求解供电网络的电路方程主要采用并行区域分解法和基于谱图稀疏化的迭代解法。区域分解法需要形成表示子区域间节点关系的稠密舒尔补矩阵,对其计算与分解的开销可能比求解原问题还大。对稀疏矩阵的迭代解法内存用量小,但迭代收敛速度与收敛性是主要的难点,近年来提出的谱图稀疏化技术构造预条件子,可以稳定地提高收敛速度,但现有工作均为串行算法的研究。

清华大学喻文健教授团队提出将区域分解与谱图稀疏化结合的方法,包括并行的谱图稀疏化、以及使用区域分解法对由稀疏子图得到预条件子进行并行求解的技术,它继承了谱图稀疏化带来的良好迭代收敛性,同时实现高效率并行计算。在一台 16 核 CPU、512GB 内存机器上的实验表明,该方法相比串行的谱图稀疏化迭代解法有 5.5 倍的平均加速,相比前人的并行供电网络仿真算法有 5.2 倍的平均加速。对一个实际的含 3.6 亿节点、42 亿条边的供电网络,它的求解用时仅为 23 分钟,比串行算法快 9.5 倍。这是首次报道在一台普通的 16 核计算机上仅用不到半小时的时间求解如此大规模的供电网络。Paper D: A Unified Framework for Layout Pattern Analysis with Deep Causal Estimation

特征尺寸的减小和制造过程的复杂性的增加导致半导体器件制造的缺陷越来越多。因此,识别缺陷布局模式的根本原因对于提高良率变得越来越重要。香港中文大学余备教授课题组联合华为诺亚方舟实验室和华为海思提出了一种基于布局感知诊断的布局模式分析框架,以有效地识别布局故障的根本原因。

在该框架的第一阶段,使用一个使用对比学习训练的编码器网络来提取布局片段的表示,这些布局片段对移位、旋转和镜像等转换是等价的,然后将其聚类形成布局模式。在第二阶段,该框架通过一个结构因果模型建立任何潜在的根本原因布局模式和系统缺陷之间的因果关系模型,然后使用该模型估计候选布局模式对系统缺陷的平均因果效应(ACE),以识别真正的根本原因。在实际工业设计中的实验结果表明,此框架在精度和速度上都优于商业工具。Paper E: HeteroCPPR: Accelerating Common Path Pessimism Removal with Heterogeneous CPU-GPU Parallelism

在芯片设计流程中,静态时序分析(STA)衡量了芯片设计的正确性和性能,是后端芯片设计和验证的核心任务之一,而静态时序分析中的公共路径悲观修正(CPPR)步骤,则保证了时序分析的准确性。缺少了 CPPR 会使分析结果过度悲观,产生虚假的错误报告,降低对芯片设计性能评估的准确性。然而,CPPR 非常缓慢,时间消耗往往以十倍到百倍计,因而限制了它的实际应用。现有的 CPPR 加速工作主要采用 CPU 上的多核并行策略。这些策略受到图算法计算模式以及 CPU 架构的限制,性能在 8-16 核心达到饱和,难以获得更大的性能提升。

北京大学林亦波教授课题组提出了 HeteroCPPR 算法,通过高效的计算任务分解策略和 GPU 算子设计,克服图算法的并行难题,在 CPU-GPU 异构计算平台上实现了 CPPR 中的图算法并行加速,首次实现多 GPU 处理大规模延时悲观量补偿和时序违例路径生成。实验结果显示,HeteroCPPR 在 4 个 GPU 上达到了 16 倍的加速,能够在 1 秒以内处理百万门级电路上的 10K-100K 路径生成问题。

三、机器之心走近全球顶尖实验室:香港中文大学EDA团队

香港中文大学 EDA 团队目前共有教授 7 人,其中IEEE院士、ACM院士 1 人(港中大工程学院院长黄定发教授),ACM杰出科学家 2 人(杨凤如教授,何宗易教授)。团队研究范围全栈式覆盖了系统设计、架构设计、逻辑物理综合、测试与验证、制造与封装等EDA领域。近六年来,团队在 EDA 领域国际顶级会议 DAC&ICCAD 共计发表论文 94 篇(系统设计 10 篇、架构设计 23 篇、逻辑物理综合 20 篇、测试与验证 21 篇、制造与封装 20 篇),位居世界前列。

除了数量众多的研究成果之外,港中文 EDA 团队还多次拿到了顶会和顶级期刊的最佳论文:

2012 DAC 最佳论文2013 ICCAD 最佳论文2015 TCAD(EDA的世界顶级期刊)最佳论文2017 ICCAD 最佳论文2021 ICCAD 最佳论文。港中文自2015年以来在DAC/ICCAD发表论文的主题分布情况。除了 EDA 两大顶级会议 DAC & ICCAD 之外,港中文 EDA 团队成员也获得 2004 年DATE、2012 年 ASPDAC、2017 年 ISPD、2020 年 ISLPED、2021 年 ASPDAC 等重要会议的年度最佳论文奖。此外,在历年 ICCAD CAD 算法竞赛产生的 30 个冠军中,香港中文大学拿到了其中的 11 个,成绩遥遥领先于世界其他顶级高校。

依据世界广泛采用的计算机科学机构的排名 CS Ranking,港中文的世界排名常年保持前列,近两年名列世界第一:

在EDA(design automation)领域,港中文、UCSD和杜克大学位列世界排名前三。大部分上榜高校都是欧美名校,在表现比较好的亚洲高校中,港中文排名第一位,北大排名12,香港城市大学第排名17,中科院和新加坡国立大学并列20。

中科大华为诺亚出手!芯片性能≠布局评分,EDA设计框架全面开源

ChipBench团队 投稿

量子位 | 公众号 QbitAI

芯片物理布局,有了直指性能指标的新测评标准!

中科大MIRA Lab和华为诺亚方舟实验室联合发布了新的评估框架和数据集,而且完全开源。

有了这套标准,布局指标与最终的端到端性能不一致、得分高而PPA性能却偏低的问题,就有望得到解决了。

在芯片设计当中,电子设计自动化 (EDA)是至关重要的一环,在业界被称为“芯片之母”,而芯片物理布局(Placement)又是其中的关键步骤。

芯片物理布局问题是一个NP-hard问题,人们尝试着通过AI来进行这项工作,但缺乏一个有效的评测标准。

传统的评估尺度——代理指标虽然易于计算,但常常与芯片最终的端到端性能存在显著差异。

为了弥补这一鸿沟,中科大MIRA Lab和华为诺亚方舟实验室联合发布了这个名为ChiPBench 的评估框架,以及相关数据集。

随着ChiPBench的上线,作者也发现了当前芯片布局算法存在很多不足,提醒相关研究人员是时候研发新算法了。

芯片设计流程面临挑战

根据“摩尔定律”,集成电路(IC)的规模发生了指数级增长,对芯片设计带来了前所未有的挑战。

为了应对这种日益增长的复杂性,EDA工具应运而生,为硬件工程师提供了极大的帮助。

EDA工具能够自动完成芯片设计工作流程中的各个步骤,包括高层次综合、逻辑综合、物理设计、测试和验证等环节。

其中,芯片布局是一个重要环节,该阶段又可以分为两个子阶段——宏布局和标准单元布局。

宏布局是超大规模集成(VLSI)物理设计中的一个关键问题,主要涉及较大元件(如SRAM和时钟发生器,通常称为宏)的排列。

这一阶段对芯片的整体布局以及线长、功耗和面积等重要设计参数具有显著影响。

之后的标准单元布局阶段,需要处理的是数量更多、体积更小的标准单元的排列问题,这些单元是数字设计的基本组成部分。

通常,该阶段利用组合优化求解等方法来实现布局摆放的优化,最大程度地减少单元间的距离,为后续的布线工作奠定良好的基础,并在一定程度上优化互联时序性能。

芯片布局传统上由人类专业设计师手工完成,这不仅耗费大量人力,而且需要大量的专家先验知识。

因此,许多设计自动化方法,尤其是基于人工智能的算法,被开发出来以实现这一过程的自动化。

然而,由于芯片设计的工作流程较长,对这些算法的评估通常集中在易于计算的中间代理指标上(例如半周长线长HPWL,布局单元密度等),但这些指标经常与端到端性能(即最终设计的 PPA)存在一定程度的偏差。

一方面,由于芯片设计工作流程的冗长,获得给定芯片布局方案的端到端性能需要大量的工程设计工作,同时作者发现直接使用现有的开源EDA工具和数据集通常无法获得端到端性能。

由于以上原因,现有的基于人工智能的芯片布局算法使用简单易得的中间代理指标来训练和评估学习到的模型。

另一方面,由于PPA指标反映了前几个阶段未充分考虑的许多方面,代理指标与最终的PPA目标之间存在严重差距 。

因此,这种差距极大地限制了现有基于人工智能的布局算法在实际工业场景中的应用。

端到端预估芯片性能

作者认为,造成这种差距的原因是早期数据集的过度简化 。

例如,广泛使用Bookshelf格式就是“过于简化”的一个代表,这种格式下的布局结果不适用于后续设计阶段,无法实现有效的最终设计。

一些后续的数据集虽然提供了运行后续阶段所需的LEF/DEF文件和必要文件,但包含的电路数量仍然有限,且缺乏某些开源工具(如OpenROAD)所需的信息。

例如,库文件中缺少时钟树综合所需的缓冲元件定义,LEF文件中的层定义不完整,这阻碍了布线阶段的工作。

为了解决这些问题,作者构建了一个包含整个流程的全面物理实现信息的数据集。

该数据集涵盖了一系列不同领域的设计,包括 CPU、GPU、网络接口、图像处理技术、物联网设备、加密单元和微控制器等组件。

作者在这些设计上执行了六种最先进的基于人工智能的芯片物理布局算法,并将每种单点算法的结果通过标准输入/输出格式接入到物理实现工作流,以获得最终的PPA结果。

初始数据集的生成以Verilog文件作为原始数据。OpenROAD执行逻辑综合,将这些高级描述转换为网表,详细描述电路元件之间的电气连接。

随后,OpenROAD的集成平面规划工具利用该网表在硅片上配置电路的物理布局。

OpenROAD将平面规划阶段产生的设计转换为LEF/DEF文件,以便于后续布局算法的应用。

同时,作者通过OpenROAD完成整个EDA设计流程,在后续阶段生成包括布局、时序树综合和布线在内的数据。

ChipBench数据集包含了物理设计流程各个阶段所需的全部设计工具包。

在评估布局阶段的算法时,前一阶段的输出文件将作为该评估算法的输入。算法处理这些输入文件,生成相应的输出文件,然后将这些输出文件集成到OpenROAD设计流程中。

最终,数据集将报告包括TNS、WNS、面积和功耗在内的性能指标,以提供全面的端到端性能评估。

这种方法提供了一套全面的评估指标,能够衡量特定阶段算法对最终芯片设计优化效果的影响,确保了评估指标的一致性,并避免了仅依赖于单一阶段简化指标的局限性。

这种评估方法有利于各种算法的优化和开发,确保了算法改进能够转化为芯片设计的实际性能提升。同时,通过一个强大的测试和改进框架,它促进了更高效、更有效的开源EDA工具的开发。

芯片布局需要开发新算法

利用上述工作流程,作者对多种基于人工智能的芯片布局算法进行了评估,包括SA、WireMask-EA、DREAMPlace、AutoDMP、MaskPlace、ChiPFormer以及OpenROAD中的默认算法。

作者对这些算法进行了端到端的评估,并报告了最终的性能指标。

另外,相关性分析结果表明,MacroHPWL与最终性能指标之间的相关性非常弱,这表明优化MacroHPWL对这些性能指标的影响非常有限。

Wirelength与WNS和TNS的相关性同样较弱。这意味着,即便某些单点算法在优化Wirelength等中间指标上取得了成功,它们在最终的物理实现中可能只能提升PPA指标的某一方面,而无法全面优化。

因此,需要寻找更合适的中间指标,以便更好地与实际的PPA目标相关联。

作者的评估结果揭示了目前主流布局算法所强调的中间指标与最终性能结果之间存在不一致性,这些发现凸显了从新的角度开发布局算法的必要性。

△不同布局算法的最差时序图

论文地址:https://arxiv.org/abs/2407.15026GitHub:https://github.com/MIRALab-USTC/ChiPBench

数据集:https://huggingface.co/datasets/ZhaojieTu/ChiPBench-D

— 完 —

量子位 QbitAI · 头条号签约

关注我们,第一时间获知前沿科技动态

相关问答

研究生发表论文都是那些,难不难发表?有温度有灵感的高校人才真经为你解答。研究生的身份是学生,但在高校科研活动中,却是一个重要的力量,承担着实验设计、执行,科研数据采集、处理等基础工作,...前...

蓝牙在物联网中有什么 应用 ?物联网 应用 好用吗?[回答]com,若有已投稿的文章可附上链接。低功耗蓝牙(BLE)智能应用,作为物联网通信技术中的短距离通信技术,已成为新的蓝海市场。看到这一行业趋势,苏州桃...

朋友们,有什么好的!广东自主研发的人工智能千变开发软件哪...[回答]叫龙芯,全名:龙芯1号芯片历史:龙芯是计算所自主研发的通用CPU,采用简单指令集,类似于MIPS指令集。龙芯1号的频率为266MHz,最早在2002年开始使用。龙...

有人说刘慈欣是单枪匹马把中国科幻文学提升到了世界级的水平,你怎么看?“刘慈欣单枪匹马把中国科幻文学提升到了世界级的水平。”这个说法的依据其实就是刘慈欣的科幻小说《三体》获得了一些国际科幻小说方面的奖项和提名,但这种说法...

你知道哪些不为人知的反人类科学?提问者谈到“被禁止的科学理论”。但是,没有所谓“被禁止的科学理论”。某些出版社为了经济利益,就在书名上胡说八道,用“被禁止的科学”“被禁止的真相”来哗...

索尼相机最新产品RX10 lV何时开售?现在已经就有卖的啊,售价12499元。RX10IV,作为索尼黑卡RX10系列的第四代产品,在核心的成像组件上RX10IV依然沿用了之前的约2010万像素1英寸ExmorRSCMOS传...

各位有什么千元级别的手机推荐,老人用?老人用的话其实现在千元的手机足够用了,现在的手机行业越来越成熟,成本也相应变低,造出来的东西同价位肯定比前几年的东西好的。首先,老年人用也就用用微信,...

中行环球通卡全国消费免手续费吗?- 汇财吧专业问答test[回答]主卡580每年,白金卡附属卡每卡RMB2000元无限卡主卡每卡RMB10000元?答,取现500:额度是1000信用卡使用收费标准是怎样的.4,是额外的钱,首年...答,取...

小狐tv在线观看(中国)IOS/手机APP官网下载V3.74.77;依赖出口时期已经结束,中国芯片时代崛起!防火墙,半导体,CPU,国防建设,半导体...AboutPCGROUP|网站介绍|隐私政策|广告服务|合作媒体|投稿指南|使.....

旅行期间用手机拍摄好还是用专业相机拍摄好?手机还是相机~这都不叫事这个很好说,手机自然无法与相机相提并论。理由如下:第一,手机数码cmos成像芯片比相机差太远,太小了,根本没有可比性,手机上看看...尤...